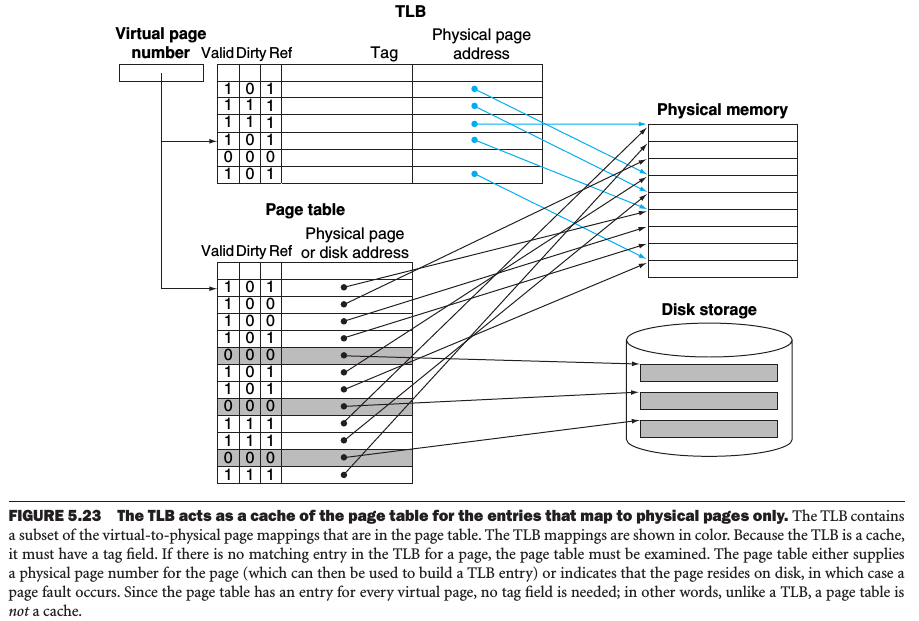

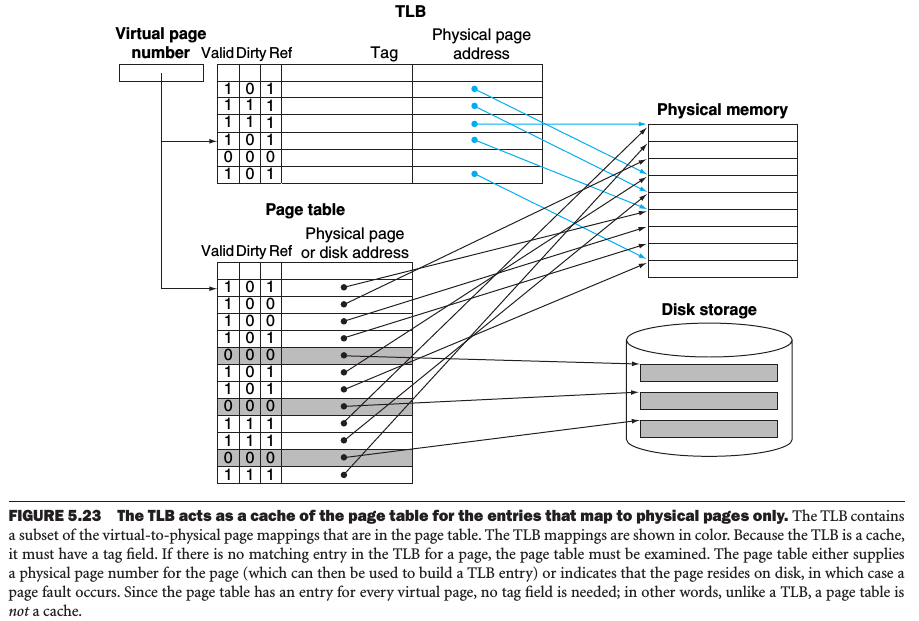

Description:

- Have to access the page table before an instruction can be fetched and before data cache/memory can be accessed is long

- Page table accesses have good locality → Cache the most recent Page Table Entry within the CPU

- Therefore, Faster Address Translation

TBL miss scenarios:

- TLB miss, page table hit

- Bring in the Page Table Entry information from page table to TLB

- Retry the access

- Usually completely performed by hardware

- TLB miss, page fault

- Bring in the page from disk (orchestrated by OS)

- Load the page table and TLB (orchestrated by OS)

- Retry the access

- Cache miss will definitely occur!